PowerCommons - The Open Silicon Commons

Welcome to PowerCommons

PowerCommons is an ambitious initiative to create the world’s first fully open, verifiable, and sovereign computing infrastructure based on the OpenPower architecture. We’re reviving and modernizing proven processor designs to deliver transparent, auditable, and secure computing platforms that serve the public interest rather than corporate surveillance.

In an era where digital infrastructure determines economic and political power, PowerCommons represents a crucial step toward technological independence and democratic control over computing resources.

What We’re Building

PowerCommons is reviving IBM’s A2O processor core—a proven 64-bit PowerPC design that powered Blue Gene/Q supercomputers—for modern FPGA platforms. We’re pairing it with Microwatt as a secure boot processor to create a fully open and verifiable SoC architecture, where every component from power-on to application execution can be inspected and audited.

Current work: A2O core revival targeting Xilinx VCU-118, with build system modernization for contemporary Vivado toolchains.

Foundation already laid: Linux booting on Microwatt/VCU-118, LiteDRAM integration, upstream contributions to the Microwatt repository.

Technical guidance: Direct collaboration with Prof. Peter Hofstee, original architect of IBM’s Cell Broadband Engine.

Where This Leads

A complete sovereign computing stack built on proven, auditable silicon—from embedded controllers through workstations to datacenter infrastructure. Not a slide deck vision: a concrete path from working FPGA implementations through formal verification to production hardware. Computing infrastructure that serves the public interest because every transistor’s behavior can be verified.

Our Vision

We’re building computing infrastructure that can be fully verified—where organizations and individuals can audit every component from silicon to software.

For government and critical infrastructure: Deploy systems where security doesn’t depend on trusting opaque vendor firmware.

For research institutions: Study and teach processor architecture with complete visibility into implementation.

For industry: Build products on foundations you can inspect, modify, and maintain independently.

The Broader Context

PowerCommons emerges from a recognition that computational infrastructure shapes society as fundamentally as roads, utilities, and communications networks. When this infrastructure is opaque and privately controlled, democratic oversight becomes impossible. We’re creating an alternative: computing as commons—collectively maintained, transparently operated, publicly auditable.

PowerCommons Development Roadmap

Long-Term Vision (2027+)

These phases depend on successful completion of the SoC platform and securing production partnerships:

- Hardware production: ASIC fabrication or volume FPGA deployment, contingent on formal verification completion and manufacturing partnerships

- Infrastructure deployment: Sovereign compute services built on verified PowerCommons hardware, contingent on hardware availability and operational partnerships

Our Mission

To democratize access to high-performance, secure, and transparent computing by creating fully open-source processor implementations and system architectures that can be verified, modified, and deployed by anyone, anywhere, without proprietary dependencies or hidden backdoors.

Project Summary

| Component | Status | Funding | Progress | Target |

|---|---|---|---|---|

| Adding VCU-118 board support to Microwatt SoC | 🟢 In Progress | Self funded | █████████░ 90% | Q3 2025 |

| PowerPC Support in LiteX SoC Framework: A Microwatt Linux Implementation on VCU-118 | 🟢 Planned | Self funded | ░░░░░░░░░░ 0% | Q4 2025 |

| From OpenPower to PowerCommons: Resurrecting and Modernizing the A2O Core | 🟡 Planning | Requested | ░░░░░░░░░░ 0% | Q2 2026 |

| PowerCommons SoC Platform | 🔵 Researching | Requested | ░░░░░░░░░░ 0% | Q2 2027 |

Why This Matters

Digital Sovereignty

Every major processor today contains hidden management engines, proprietary firmware, and un-auditable code paths. PowerCommons changes this paradigm by ensuring every transistor’s behavior can be inspected and verified.

Post-Surveillance Computing

In alignment with post-capitalist visions of technology, PowerCommons creates computing infrastructure that serves communities rather than extracting value from them.

Technological Commons

Like public utilities and infrastructure, fundamental computing technology should be a commons - collectively owned, transparently operated, and democratically governed.

Get Involved

For Developers

- Code Repository: codeberg.org/PowerCommons

- Get Started: Getting Started Guide

- Matrix Chat: #powercommons:matrix.org

For Organizations

- Government & Critical Infrastructure: Deploy verifiable, sovereign computing

- Academic Institutions: Research and teach with fully transparent systems

- Industry Partners: Build secure products on open foundations

For Citizens

- Learn: Understand why open hardware matters for democracy

- Advocate: Support policies promoting open infrastructure

- Support: Contribute to sustainable development

Partners

- OpenPower Foundation - Technical guidance and community

- The Commune - Digital sovereignty advocacy on Medium

- The Sovereign Workshop - Meetups, Tutorials and how to articles on building the sovereign stack. Coming soon.

Updates

February, 2026: Pre-built bitstreams and Linux images published

New features include VCU-118 DRAM support on Microwatt SoC, Linux Boot on Litex SoC.

February, 2026: PowerCommons SoC Proposal Submitted

Submitted NLNET funding proposal for PowerCommons SoC

September 30, 2025: NLnet Funding Proposals Submitted

Submitted NLNET funding proposal for A2O Core revival.

September 20, 2025: First Microwatt boot with LiteDRAM, clock and timing issues..

August 2025: MicroWatt VCU118 Success

Successfully booted Linux on VCU118 platform without DRAM.

July 2025: Project Inception

PowerCommons initiative launched with support from OpenPower Foundation.

PowerCommons is a public interest technology initiative aligned with European digital sovereignty goals and the principles of the commons.

Mission & Vision

Our Mission

To democratize high-performance computing by creating fully open, transparent, and verifiable processor architectures that serve as digital commons - collectively owned, democratically governed, and accessible to all.

PowerCommons develops and maintains open-source processor implementations, system architectures, and supporting infrastructure that eliminate proprietary dependencies, hidden functionalities, and corporate control over fundamental computing resources.

Our Vision

A Future of Sovereign Computing

We envision a world where:

- Every circuit is inspectable - No hidden management engines, no proprietary firmware, no unauditable code paths

- Communities control their infrastructure - Local sovereignty over digital resources, not dependency on foreign corporations

- Innovation serves humanity - Technology development guided by public interest, not surveillance capitalism

- Knowledge is truly free - Complete transparency from transistor to application, enabling genuine understanding and innovation

Join the Revolution

PowerCommons isn’t just building processors - we’re building the foundation for a democratic digital future. Every contribution, whether code, documentation, advocacy, or funding, advances our collective liberation from corporate control over computing.

The power of computing belongs to the people.

Get Involved

🛠️ Developers: Contribute code and documentation

📚 Educators: Teach open hardware principles

🏛️ Policymakers: Support sovereign computing initiatives

💰 Funders: Invest in democratic technology

🗣️ Advocates: Spread the word about digital sovereignty

“The master’s tools will never dismantle the master’s house. We must build our own tools - transparent, democratic, and free.”

— Adapted from Audre Lorde for the digital age

Digital Sovereignty

Reclaiming Control Over Our Digital Infrastructure

Digital sovereignty is not merely about data localization or regulatory compliance - it’s about fundamental democratic control over the technologies that increasingly govern our lives. PowerCommons embodies this principle by creating computing infrastructure that communities can truly own, understand, and control.

The Crisis of Technological Dependence

Hidden Control Mechanisms

Every modern processor contains multiple layers of proprietary control:

- Management Engines: Intel ME, AMD PSP run below the operating system with full system access

- Proprietary Firmware: Unauditable code controlling critical functions

- Hardware Backdoors: Undocumented features accessible to manufacturers

- Supply Chain Vulnerabilities: Components from untrusted sources with unknown modifications

These mechanisms create fundamental vulnerabilities that no amount of software security can address.

Economic Extraction

The current computing paradigm extracts value through:

- Planned Obsolescence: Artificial limitations forcing constant upgrades

- Vendor Lock-in: Proprietary standards preventing migration

- Surveillance Capitalism: Data extraction as primary business model

- Rent-Seeking: Software-as-a-Service replacing ownership

PowerCommons breaks these extraction patterns by ensuring permanent ownership and control.

Technical Foundations of Sovereignty

Verifiable Security

True sovereignty requires the ability to verify every aspect of the system:

- Open Hardware: Every logic gate documented and inspectable

- Reproducible Builds: Identical outputs from source code

- Formal Verification: Mathematical proofs of security properties

- Transparent Supply Chain: Known origin of every component

Technological Independence

PowerCommons achieves independence through:

- No Proprietary Dependencies: Fully open stack from silicon to application

- Local Manufacturing Capability: Designs suitable for diverse fab processes

- Knowledge Transfer: Complete documentation and education

- Tool Chain Freedom: Open development tools throughout

Call to Action

For Policymakers

- Mandate Open Hardware: Require transparency in public procurement

- Fund Development: Support open processor initiatives

- Create Standards: Establish sovereignty requirements

- Build Capacity: Invest in local manufacturing

For Technologists

- Contribute Code: Develop open implementations

- Share Knowledge: Document and teach

- Build Tools: Create development infrastructure

- Form Networks: Connect with aligned projects

For Citizens

- Demand Transparency: Require open systems in public services

- Support Development: Contribute to funding campaigns

- Learn and Share: Understand and explain the importance

- Organize Locally: Build community technology initiatives

Resources

Essential Reading

- “The Age of Surveillance Capitalism” - Shoshana Zuboff

- “Radical Technologies” - Adam Greenfield

- “The Stack” - Benjamin Bratton

- “Platform Capitalism” - Nick Srnicek

Pioneering Organizations

- European Digital Rights (EDRi)

- Free Software Foundation Europe

- Chaos Computer Club

- La Quadrature du Net

Policy Documents

- EU Digital Sovereignty Strategy

- German Sovereign Tech Fund Charter

- Barcelona Digital Sovereignty Plan

- Amsterdam Digital Agenda

“Technology is the answer, but what was the question?”

— Cedric Price

The question is: How do we build technology that serves humanity rather than exploiting it? PowerCommons provides one answer: through radical transparency, democratic control, and the commons model.

Digital sovereignty is not a destination but a continuous process of reclaiming control over our technological future. Join us in building infrastructure for human flourishing rather than corporate extraction.

Why OpenPower

The Foundation for True Computing Freedom

A Proven Architecture with Deep Roots

OpenPower isn’t just another instruction set architecture - it’s a battle-tested technology with over 30 years of deployment in mission-critical systems. From the servers running banking infrastructure to the supercomputers modeling climate change, Power architecture has proven its reliability at scale.

Unlike emerging architectures that promise future potential, OpenPower delivers today with:

- Mature ecosystem: Decades of software support, tools, and expertise

- Production proven: Powers enterprise workloads globally

- Performance leadership: Consistently ranks in supercomputing top500

- Open governance: True community control through OpenPower Foundation

Comparison Matrix

| Feature | OpenPower | RISC-V | ARM | x86 |

|---|---|---|---|---|

| ISA License | Open | Open | Proprietary | Proprietary |

| Open Implementations | Yes (Multiple) | Few | No | No |

| Ecosystem Maturity | 30+ years | <10 years | 20+ years | 40+ years |

| Linux Support | Excellent | Growing | Excellent | Excellent |

| Enterprise Deployment | Widespread | Limited | Growing | Dominant |

| Formal Verification | Possible | Possible | Difficult | Impossible |

| Patent Protection | OPF Pool | Fragmented | ARM Ltd | Intel/AMD |

| Community Governance | Yes | Partial | No | No |

Technical Superiority

Architecture Advantages

64-bit from the Ground Up

Power was designed as a 64-bit architecture from inception, not retrofitted like x86. This clean design yields:

- Consistent instruction encoding

- Efficient memory addressing

- Superior virtualization capabilities

- Hardware-enforced security boundaries

RISC Philosophy Done Right

- Fixed-length instructions for predictable decode

- Large register file (32 general purpose registers)

- Simple, orthogonal instruction set

- Powerful load/store architecture

Advanced Features

- Hardware transactional memory

- Decimal floating-point in hardware

- Advanced SIMD capabilities (VSX)

- Sophisticated branch prediction

Performance Characteristics

OpenPower processors excel in:

- Throughput Computing: Multiple execution units and deep pipelines

- Memory Bandwidth: Advanced cache hierarchies and memory controllers

- Parallel Processing: SMT4/SMT8 simultaneous multithreading

- Enterprise Reliability: ECC throughout, hardware error recovery

True Openness

While other architectures claim openness, OpenPower delivers:

| Architecture | License Model | Implementation |

|---|---|---|

| RISC-V | Open ISA | Most implementations proprietary |

| OpenPower | Open ISA | Open implementations (Microwatt, A2O) |

| ARM | Proprietary, expensive licenses | Heavily restricted |

| OpenPower | Royalty-free | No restrictions |

| x86 | Completely closed | Legally protected |

| OpenPower | Community-driven | Open governance |

Verification and Trust

With OpenPower’s open implementations:

- Every gate can be inspected

- No hidden backdoors possible

- Formal verification feasible

- Reproducible builds from source

Advisory Board

Leadership & Governance

PowerCommons operates under a collaborative governance model that balances technical expertise with democratic participation, ensuring our technology serves the public interest.

Advisory Board / Mentors

Prof. Peter Hofstee

Chief Technical Advisor

Distinguished Research Staff Member, IBM | Professor, Delft University of Technology

Prof. Peter Hofstee is a distinguished research staff member at IBM Austin and part-time professor in Big Data Systems at Delft University of Technology. He is best known as chief architect of the Synergistic Processor Elements in the Cell Broadband Engine processor, used in Sony’s PlayStation 3 and IBM’s Roadrunner supercomputer — the first system to achieve sustained petaflop operation in 2008. The A2 processor family — including the A2O core that PowerCommons aims to revive—was developed following IBM’s game console processor designs: the Xbox 360 processor and Hofstee’s Cell processor for the PlayStation 3. Prof. Hofstee’s pioneering work on the Cell architecture directly influenced the A2 family’s design philosophy. His decades of experience in high-performance heterogeneous computing and deep knowledge of the architectural lineage connecting Cell to A2O make him uniquely qualified to guide PowerCommons’ technical strategy for reviving and modernizing the A2O core for contemporary applications including AI workloads and open-source supercomputing.

Ganesan Narayanasamy

Mentor and Community Advisor

President, OpenPower Foundation | CEO - ObjectAutomation Inc..

Ganesan Narayanasamy is a technology leader with nearly three decades of experience at IBM, where he held leadership positions focused on high-performance computing, chip design, and artificial intelligence. He was instrumental in driving the OpenPOWER and AI ecosystem initiatives, with emphasis on partner enablement and market development, creating training programs for partners and supporting emerging market opportunities worldwide.

As President of the OpenPOWER Foundation and CEO of Object Automation System Solutions Inc., Ganesan leads global initiatives to expand the OpenPOWER ecosystem through academic partnerships and industry collaboration. He actively collaborates with leading institutions including IIT Madras, IIT Roorkee, and IIT Ropar on Microwatt and chip design education initiatives ObjectAutomation, making him ideally positioned to guide PowerCommons’ technical direction and ecosystem development.

His extensive experience in ecosystem building, partner enablement, and academic outreach provides PowerCommons with critical strategic guidance for community engagement, institutional partnerships, and long-term sustainability planning.

Partner Organizations

Institutional Partners

- OpenPower Foundation - Technical standards and ecosystem

Advisors We Seek to Engage

PowerCommons is actively reaching out to thought leaders and policy makers who can help advance digital sovereignty:

Policy & Government Leaders

Margrethe Vestager

Executive Vice-President, European Commission

A Europe Fit for the Digital Age

Roberto Viola

Director-General, DG CONNECT

European Commission digital policy

Cédric O

Former French Secretary of State for Digital

European tech sovereignty advocate

Marina Kaljurand

MEP, Former Estonian Foreign Minister

Digital rights and cybersecurity

Technology & Innovation

Mitchell Baker

CEO, Mozilla Corporation

Open internet and technology democracy

Eben Moglen

Columbia Law School, Software Freedom Law Center

Free software legal frameworks

Bruce Schneier

Harvard Kennedy School

Security technologist and policy fellow

Zeynep Tufekci

Columbia University

Technology and society researcher

Economic & Social Innovation

Mariana Mazzucato

UCL Institute for Innovation

Mission-oriented innovation and public value

Kate Raworth

Oxford University

Doughnut economics and regenerative design

Evgeny Morozov

Technology critic and researcher

Digital sovereignty and platform regulation

Trebor Scholz

The New School

Platform cooperativism

If you have connections to these leaders or similar advocates for digital sovereignty, please help us make contact

Community Partners

Building the Liberation Technology Ecosystem

PowerCommons thrives through collaboration with aligned organizations, communities, and initiatives working toward technological sovereignty, digital rights, and the commons.

Institutional Partners

OpenPower Foundation

Role: Technical Standards & Governance

Contribution: Architecture specifications, compliance testing, ecosystem coordination

Contact: openpowerfoundation.org

The OpenPower Foundation provides the technical and legal framework that makes PowerCommons possible. Their open governance model and patent pool ensure our work remains free and unencumbered.

How to Become a Partner

For Organizations

- Align with PowerCommons values and mission

- Identify collaboration opportunities

- Connect via [email protected]

- Contribute through code, resources, or advocacy

- Amplify the message of liberation technology

For Individuals

Join as a community partner by:

- Contributing code or documentation

- Organizing local events

- Translating materials

- Advocating for open hardware

- Teaching and mentoring

Partnership Principles

- Mutual Aid: Support flows in all directions

- Transparency: Open collaboration and communication

- Autonomy: Partners maintain independence

- Solidarity: United in liberation technology

- Sustainability: Long-term thinking and commitment

Current Needs

We’re actively seeking partners in:

- 🎓 Academic Research: Formal verification, security analysis

- 🏭 Manufacturing: PCB fabrication, ASIC production

- 💰 Funding: Grants, donations, sustainable revenue

- 🌍 Global Reach: Regional coordinators and translators

- 🛠️ Technical: FPGA experts, compiler developers

- 📢 Advocacy: Policy influence, public awareness

Partnership Benefits

- Early access to technology developments

- Influence on project direction

- Recognition in project materials

- Collaboration opportunities

- Shared resources and knowledge

- Building the commons together

Quick Start

Get Microwatt running on Litex Soc and boot Linux on Xilinx VCU 118 FPGA in under 30 minutes using prebuilt resources.

💬 Need Help? Stuck or have questions? Join #powercommons:matrix.org for real-time support from the community!

Prerequisites

- FPGA board with USB cable - we’ve only tested Xilinx VCU-118. Arty A7 100T support coming soon.

- You have already setup a PowerCommons WSL instance following the WSL Setup instructions or have an equivalent Linux setup.

- Vivado is not required for quickstart.

Steps

1. Download Prebuilt Bitstream and Linux images

Depending upon your end goal, download the corresponding bitstream. For example, if you want to see linux boot on the VCU 118 board with Litex SoC, download the following bitstream and linux image: For Xilinx VCU 118, download the following bitstream:

Download bitstream for Microwatt on Litex SoC microwatt-litex-vcu118-dram-2026-02-25.bit:

curl -O https://codeberg.org/PowerCommons/Releases/releases/download/vcu118-20260225/microwatt-litex-vcu118-dram-2026-02-25.bit

Download linux:

curl -O https://codeberg.org/PowerCommons/Releases/releases/download/vcu118-20260225/linux-6.12.0-litex-2026-02-25.dtbImage.microwatt.elf

2. Program the bitstream:

openFPGALoader -b vcu118 microwatt-litex-vcu118-dram-2026-02-25.bit

Check to see is serial/console is up:

litex_term /dev/ttyUSB2

You should see either DRAM initialization or the litex bios depending upon how quickly you connect to the console after flashing:

+==========================================+

| P O W E R C O M M O N S |

| Microwatt PPC64LE | LiteX SoC |

+==========================================+

__ _ __ _ __

/ / (_) /____ | |/_/

/ /__/ / __/ -_)> <

/____/_/\__/\__/_/|_|

Build your hardware, easily!

(c) Copyright 2012-2025 Enjoy-Digital

(c) Copyright 2007-2015 M-Labs

BIOS built on Feb 25 2026 02:02:36

BIOS CRC passed (9ccc6cfa)

LiteX git sha1: 69f48eb98

--=============== SoC ==================--

CPU: Microwatt @ 125MHz

BUS: wishbone 32-bit @ 4GiB

CSR: 32-bit data little ordering

ROM: 128.0KiB

SRAM: 8.0KiB

L2: 8.0KiB

SDRAM: 2.0GiB 64-bit @ 1000MT/s (CL-9 CWL-9)

MAIN-RAM: 1.0GiB

--========== Initialization ============--

Initializing SDRAM @0x00000000...

Switching SDRAM to software control.

Write leveling:

tCK equivalent taps: 592

Cmd/Clk scan (0-296)

|10000 |10000 |11000 |11110| best: 0

Setting Cmd/Clk delay to 0 taps.

Data scan:

m0: |00000000000001111111111| delay: 195

m1: |00000000000111111111111| delay: 162

m2: |00000000000000000111111| delay: 262

m3: |00000000000000000001111| delay: 293

m4: |10000000000000000000111| delay: 307

m5: |00000000000000000001111| delay: 295

m6: |10000000000000000001111| delay: 304

m7: |11000000000000000000011| delay: 326

Write latency calibration:

m0:0 m1:0 m2:0 m3:0 m4:0 m5:0 m6:0 m7:0

Read leveling:

m0, b00: |00000000000000000000000000000000| delays: -

m0, b01: |11100000000000000000000000000000| delays: 18+-18

m0, b02: |00000000111111111111110000000000| delays: 226+-114

m0, b03: |00000000000000000000000000111111| delays: 461+-50

m0, b04: |00000000000000000000000000000000| delays: -

m0, b05: |00000000000000000000000000000000| delays: -

m0, b06: |00000000000000000000000000000000| delays: -

m0, b07: |00000000000000000000000000000000| delays: -

best: m0, b02 delays: 225+-113

m1, b00: |00000000000000000000000000000000| delays: -

m1, b01: |11100000000000000000000000000000| delays: 19+-19

m1, b02: |00000000111111111111000000000000| delays: 218+-105

m1, b03: |00000000000000000000000000111111| delays: 458+-52

m1, b04: |00000000000000000000000000000000| delays: -

m1, b05: |00000000000000000000000000000000| delays: -

m1, b06: |00000000000000000000000000000000| delays: -

m1, b07: |00000000000000000000000000000000| delays: -

best: m1, b02 delays: 218+-105

m2, b00: |00000000000000000000000000000000| delays: -

m2, b01: |00000000000000000000000000000000| delays: -

m2, b02: |00011111111111111000000000000000| delays: 155+-112

m2, b03: |00000000000000000000011111111111| delays: 423+-88

m2, b04: |00000000000000000000000000000000| delays: -

m2, b05: |00000000000000000000000000000000| delays: -

m2, b06: |00000000000000000000000000000000| delays: -

m2, b07: |00000000000000000000000000000000| delays: -

best: m2, b02 delays: 154+-112

m3, b00: |00000000000000000000000000000000| delays: -

m3, b01: |00000000000000000000000000000000| delays: -

m3, b02: |00000111111111111110000000000000| delays: 176+-112

m3, b03: |00000000000000000000000111111111| delays: 434+-76

m3, b04: |00000000000000000000000000000000| delays: -

m3, b05: |00000000000000000000000000000000| delays: -

m3, b06: |00000000000000000000000000000000| delays: -

m3, b07: |00000000000000000000000000000000| delays: -

best: m3, b02 delays: 177+-114

m4, b00: |00000000000000000000000000000000| delays: -

m4, b01: |00000000000000000000000000000000| delays: -

m4, b02: |11111111111100000000000000000000| delays: 92+-92

m4, b03: |00000000000000001111111111111100| delays: 361+-110

m4, b04: |00000000000000000000000000000000| delays: -

m4, b05: |00000000000000000000000000000000| delays: -

m4, b06: |00000000000000000000000000000000| delays: -

m4, b07: |00000000000000000000000000000000| delays: -

best: m4, b03 delays: 363+-111

m5, b00: |00000000000000000000000000000000| delays: -

m5, b01: |00000000000000000000000000000000| delays: -

m5, b02: |11111111100000000000000000000000| delays: 68+-68

m5, b03: |00000000000000111111111111100000| delays: 322+-102

m5, b04: |00000000000000000000000000000000| delays: 509+-02

m5, b05: |00000000000000000000000000000000| delays: -

m5, b06: |00000000000000000000000000000000| delays: -

m5, b07: |00000000000000000000000000000000| delays: -

best: m5, b03 delays: 319+-103

m6, b00: |00000000000000000000000000000000| delays: -

m6, b01: |00000000000000000000000000000000| delays: -

m6, b02: |11111111111111000000000000000000| delays: 110+-110

m6, b03: |00000000000000000001111111111111| delays: 398+-107

m6, b04: |00000000000000000000000000000000| delays: -

m6, b05: |00000000000000000000000000000000| delays: -

m6, b06: |00000000000000000000000000000000| delays: -

m6, b07: |00000000000000000000000000000000| delays: -

best: m6, b02 delays: 108+-108

m7, b00: |00000000000000000000000000000000| delays: -

m7, b01: |00000000000000000000000000000000| delays: -

m7, b02: |00111111111111000000000000000000| delays: 123+-101

m7, b03: |00000000000000000000111111111111| delays: 413+-97

m7, b04: |00000000000000000000000000000000| delays: -

m7, b05: |00000000000000000000000000000000| delays: -

m7, b06: |00000000000000000000000000000000| delays: -

m7, b07: |00000000000000000000000000000000| delays: -

best: m7, b02 delays: 124+-103

Switching SDRAM to hardware control.

Memtest at 0 (2.0MiB)...

Write: 0x0-0x200000 2.0MiB

Read: 0x0-0x200000 2.0MiB

Memtest OK

Memspeed at 0 (Sequential, 2.0MiB)...

Write speed: 117.2MiB/s

Read speed: 151.8MiB/s

Setting up exception vectors... done.

--============== Boot ==================--

Booting from serial...

Press Q or ESC to abort boot completely.

sL5DdSMmkekro

Timeout

No boot medium found

--============= Console ================--

litex>

Press ctrl-c twice to exit.

3. Load Linux

litex_term --kernel linux-6.12.0-2026-litex-02-25.dtbImage.microwatt.elf --kernel-adr 0x5000000 --serial-boot /dev/ttyUSB2

Replace /dev/ttyUSB2 wit your USB console output. Press enter two times after the command and you will see a litex console. Type serialbootand press enter. Your screen should like below with login shell at the end:

litex> serialboot

Booting from serial...

Press Q or ESC to abort boot completely.

sL5DdSMmkekro

[LITEX-TERM] Received firmware download request from the device.

[LITEX-TERM] Uploading /home/powercommons/bitstreams/linux-6.12.0-litex-2026-02-25.dtbImage.microwatt.elf to 0x05000000 (5082344 bytes)...

[LITEX-TERM] Upload calibration... (inter-frame: 10.00us, length: 64)

[LITEX-TERM] Upload complete (9.9KB/s).

[LITEX-TERM] Booting the device.

[LITEX-TERM] Done.

ELF: Valid PPC64LE binary, entry=0x01300000

ELF: Loading segment 0: 0x004c6400 bytes to 0x1300000

Executing booted program at 0x01300000

--============= Liftoff! ===============--

[ 0.000000] dt-cpu-ftrs: setup for ISA 3000

[ 0.000000] dt-cpu-ftrs: final cpu/mmu features = 0x0000008380039181 0x20005040

[ 0.000000] radix-mmu: Page sizes from device-tree:

[ 0.000000] radix-mmu: Page size shift = 12 AP=0x0

[ 0.000000] radix-mmu: Page size shift = 16 AP=0x5

[ 0.000000] radix-mmu: Page size shift = 21 AP=0x1

[ 0.000000] radix-mmu: Page size shift = 30 AP=0x2

[ 0.000000] radix-mmu: Mapped 0x0000000000000000-0x0000000001400000 with 2.00 MiB pages (exec)

[ 0.000000] radix-mmu: Mapped 0x0000000001400000-0x0000000020000000 with 2.00 MiB pages

[ 0.000000] radix-mmu: Initializing Radix MMU

[ 0.000000] Linux version 6.12.0 (powercommons@DESKTOP-ECRAP4O) (powerpc64le-buildroot-linux-gnu-gcc.br_real (Buildroot 2025.02.10-51-g4df2c68d0f-dirty) 13.4.0, GNU ld (GNU Binutils) 2.43.1) #2 Wed Feb 25 02:12:35 EET 2026

[ 0.000000] Hardware name: Microwatt 0x630000 microwatt

[ 0.000000] -----------------------------------------------------

[ 0.000000] phys_mem_size = 0x20000000

[ 0.000000] dcache_bsize = 0x40

[ 0.000000] icache_bsize = 0x40

[ 0.000000] cpu_features = 0x0000008380039181

[ 0.000000] possible = 0x001ffbebcb5fb185

[ 0.000000] always = 0x0000000380008181

[ 0.000000] cpu_user_features = 0xcc002102 0x88800000

[ 0.000000] mmu_features = 0x20005040

[ 0.000000] firmware_features = 0x0000000000000000

[ 0.000000] vmalloc start = 0xc008000000000000

[ 0.000000] IO start = 0xc00a000000000000

[ 0.000000] vmemmap start = 0xc00c000000000000

[ 0.000000] -----------------------------------------------------

[ 0.000000] barrier-nospec: using ORI speculation barrier

[ 0.000000] Zone ranges:

[ 0.000000] Normal [mem 0x0000000000000000-0x000000001fffffff]

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000000000000-0x000000001fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000000000000-0x000000001fffffff]

[ 0.000000] Kernel command line:

[ 0.000000] Dentry cache hash table entries: 65536 (order: 7, 524288 bytes, linear)

[ 0.000000] Inode-cache hash table entries: 32768 (order: 6, 262144 bytes, linear)

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 131072

[ 0.000000] mem auto-init: stack:all(zero), heap alloc:off, heap free:off

[ 0.000000] SLUB: HWalign=128, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 16

[ 0.000000] ICS native initialized for sources 16..31

[ 0.000000] ICS native backend registered

[ 0.000144] time_init: 64 bit decrementer (max: 7fffffffffffffff)

[ 0.000292] clocksource: timebase: mask: 0xffffffffffffffff max_cycles: 0x39a85c4118, max_idle_ns: 881590405314 ns

[ 0.000479] clocksource: timebase mult[4000000] shift[23] registered

[ 0.002451] pid_max: default: 32768 minimum: 301

[ 0.004559] Mount-cache hash table entries: 1024 (order: 1, 8192 bytes, linear)

[ 0.004889] Mountpoint-cache hash table entries: 1024 (order: 1, 8192 bytes, linear)

[ 0.042938] Memory: 474044K/524288K available (4364K kernel code, 460K rwdata, 12020K rodata, 2220K init, 306K bss, 49052K reserved, 0K cma-reserved)

[ 0.047762] devtmpfs: initialized

[ 0.095252] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.095558] futex hash table entries: 256 (order: 0, 6144 bytes, linear)

[ 0.116811] NET: Registered PF_NETLINK/PF_ROUTE protocol family

[ 0.143887] platform soc@c0000000: Fixed dependency cycle(s) with /soc@c0000000/interrupt-controller@bff1000

[ 0.150267] platform soc@c0000000: Fixed dependency cycle(s) with /soc@c0000000/interrupt-controller@bff1000

[ 0.197569] pps_core: LinuxPPS API ver. 1 registered

[ 0.197695] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <[email protected]>

[ 0.198289] PTP clock support registered

[ 0.216145] clocksource: Switched to clocksource timebase

[ 0.245834] NET: Registered PF_INET protocol family

[ 0.249281] IP idents hash table entries: 8192 (order: 4, 65536 bytes, linear)

[ 0.263361] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 4096 bytes, linear)

[ 0.263712] Table-perturb hash table entries: 65536 (order: 6, 262144 bytes, linear)

[ 0.264177] TCP established hash table entries: 4096 (order: 3, 32768 bytes, linear)

[ 0.264911] TCP bind hash table entries: 4096 (order: 4, 65536 bytes, linear)

[ 0.267771] TCP: Hash tables configured (established 4096 bind 4096)

[ 0.269531] UDP hash table entries: 256 (order: 1, 8192 bytes, linear)

[ 0.269895] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes, linear)

[ 0.272103] NET: Registered PF_UNIX/PF_LOCAL protocol family

[ 0.298495] workingset: timestamp_bits=62 max_order=17 bucket_order=0

[ 0.316858] io scheduler mq-deadline registered

[ 0.317280] io scheduler bfq registered

[ 0.348307] Serial: 8250/16550 driver, 4 ports, IRQ sharing disabled

[ 0.411624] c8003800.serial: ttyLXU0 at MMIO 0x0 (irq = 16, base_baud = 0) is a liteuart

[ 0.412114] printk: legacy console [liteuart0] enabled

[ 1.745740] brd: module loaded

[ 1.981850] loop: module loaded

[ 2.010726] NET: Registered PF_INET6 protocol family

[ 2.068458] Segment Routing with IPv6

[ 2.072120] In-situ OAM (IOAM) with IPv6

[ 2.076406] sit: IPv6, IPv4 and MPLS over IPv4 tunneling driver

[ 2.121932] NET: Registered PF_PACKET protocol family

[ 2.682557] clk: Disabling unused clocks

[ 3.877907] Freeing unused kernel image (initmem) memory: 2220K

[ 3.893489] Run /init as init process

Saving 256 bits of non-creditable seed for next boot

Starting syslogd: OK

Starting klogd: OK

Running sysctl: OK

Starting network: OK

Starting crond: OK

+==========================================+

| P O W E R C O M M O N S |

| Microwatt PPC64LE | LiteX SoC |

| Xilinx VCU-118 |

| [email protected] |

+==========================================+

vcu118-litex-microwatt login:

See Release for other images.

Next Steps

No FPGA Hardware?

Use University of Oregon remote systems - free access for developers

Pre-Built Bit Streams

Development Environment

This page lists the minimum requirements for setting up the development toolchain as well as various tooling that’s required to build PowerCommons projects.

Minimum requirements and supported configurations

Currently, PowerCommons is only supported on X86/64 bit systems as 32 bit systems are limited to 4 GB in memory. There are workarounds available, but they are not officially supported or tested by the PowerCommons project.

Vivado is supported on the following operating systems on x86-64 processor architectures:

- Microsoft Windows Professional/Enterprise 10.0 22H2 Update

- Microsoft Windows 11.0 23H2 and 24H2 Update

- Red Hat Enterprise Workstation/Server 8.10, 9.4, 9.5, 9.6, and 10.0 (64-bit), English

- SUSE Linux Enterprise 15 SP4,15 SP6, and 15 SP7 (64-bit), English

- Amazon Linux 2 AL2023 LTS (64-bit)

- AlmaLinux 8.10, 9.4, 9.5, 9.6, and 10.0 (64-bit)

- Ubuntu Linux 22.04.3, 22.04.4, 22.04.5, 24.04, 24.04.1, and 24.04.2 (64-bit), English

- Rocky Linux 8.10, 9.6, and 10.0

Minimum Recommended Memory

We recommend a minimum of 32 GB of RAM for all PowerCommons related work. Technically, its possible to get the builds working for smaller FPGAs i.e. Arty A7 with 16 GB memory, but the builds will be painfully slow. Instead of wasting your time on slower systems, you can request access to our University of Oregon systems with powerful workstations and fully configured environment.

If you are building for any of the larger FPGA’s such as Xilinx VCU 118, we recommend at least 128 GB of RAM. Memory requirements for building for various boards are listed here

Common tooling - Required for all projects

You need to setup the following tools for all PowerCommon projects including Microwatt enhancements, A2O Revival and for A2O ISA Upgrade project. Installation and setup instructions for each of these components are also linked below. If you find an issue with the documentatinon, please open a ticket in our repository.

| Tool | Purpose | Install Time | Installation Instructions |

|---|---|---|---|

| WSL/Linux | Base environment | 10 min | WSL Installation |

| Vivado 2025.x | FPGA synthesis | 60 min | Vivado Installation |

| Git, tio, OpenFPGALoader, OpenOCD | Code versioning | 1 minute | Utilities |

Note

It is recommended to use the provided WSL setup script instead of setting up your on environment. It has all the necessary tooling and can get you running in no time.

Microwatt

If you are planning to work with the Microwatt codebase, you additionally need the following tools:

| Tool | Purpose | Install Time |

|---|---|---|

| FuseSoc | Microwatt’s native build system | 10 min |

| OpenFPGALoader | Used for flashing bitstreams and Linux kernel | 10 min |

Note

The WSL script automatically installs these and no additional setup is required.

A2O - Revival and Upgrade

| Tool | Purpose | Install Time |

|---|

No special tooling needed just yet.

Support

Issues? See Troubleshooting

WSL2 Ubuntu Setup

While not strictly a requirement, your development workflow might benefit from creating multiple WSL environments instead of using one environment for everything. By having multiple instances, you can cleanly isolate libraries, dependencies etc. and restart from clean state if need.

Installing WSL2 on Windows

This step is only required for Windows users. Linux users can skip this step. Before you continue with the steps below, make sure you have a working WSL 2 installation. For instructions on installing WSL 2 on Windows, follow the instructions on Microsoft’s website.

Next, verify that your WSL 2 installation. Open a Windows terminal or powershell and key in the wsl --version. You should see output similar to the following. Make sure your WSL version is also over 2.

> wsl --version

WSL version: 2.5.7.0

Kernel version: 6.6.87.1-1

WSLg version: 1.0.66

MSRDC version: 1.2.6074

Direct3D version: 1.611.1-81528511

DXCore version: 10.0.26100.1-240331-1435.ge-release

Windows version: 10.0.26100.7171

PowerCommons Ubuntu WSL Image - Automated Installation

You can use the following script to provision a complete WSL development environment for the PowerCommons project that includes all development dependencies, Litex, FuseSoc, OpenOCD etc.

Note

If you want to find your home directory, run the following in PowerShell:

echo $env:USERPROFILE

To use this script, create a folder called .cloud-init in your Windows $HOME folder. Create a file called Ubuntu-24.04.user-data inside this folder and copy paste the following contents in this file:

#cloud-config

locale: en_US

users:

- name: powercommons

gecos: Power Commons

groups: [adm,dialout,cdrom,floppy,sudo,audio,dip,video,plugdev,netdev]

sudo: ALL=(ALL) NOPASSWD:ALL

shell: /bin/bash

write_files:

- path: /etc/wsl.conf

append: true

content: |

[user]

default=powercommons

packages: [git, libc6-dev-i386, net-tools, graphviz, make, unzip, zip, g++,

xvfb, libnss3-dev, libgdk-pixbuf2.0-dev, libgtk-3-dev,

libxss-dev, libasound2-dev, openssl, fdisk, libsecret-1-dev, curl, wget,

build-essential, libssl-dev, zlib1g-dev, libbz2-dev, libreadline-dev, libsqlite3-dev,

libncurses-dev, xz-utils, tk-dev, libxml2-dev, libxmlsec1-dev, libffi-dev, liblzma-dev, libzstd-dev, tio,

cmake, ninja-build, ccache, autoconf, automake, libtool, pkg-config, gcc-powerpc64le-linux-gnu, g++-powerpc64le-linux-gnu,

binutils-powerpc64le-linux-gnu, flex, bison, bc, libssl-dev, libelf-dev, device-tree-compiler, qemu-system-ppc64, openocd]

runcmd:

- sudo apt update && sudo apt -y upgrade

- sudo git clone https://github.com/Microsoft/vcpkg.git /opt/vcpkg

- /opt/vcpkg/bootstrap-vcpkg.sh

- su - powercommons -c 'curl -fsSL https://pyenv.run | bash'

- su - powercommons -c 'curl -s https://ohmyposh.dev/install.sh | bash -s'

- su - powercommons -c 'ssh-keygen -t ed25519 -N "" -f ~/.ssh/id_ed25519'

# Write all bashrc entries

- |

su - powercommons -c 'cat >> ~/.bashrc << "EOF"

export PYENV_ROOT="$HOME/.pyenv"

[[ -d $PYENV_ROOT/bin ]] && export PATH="$PYENV_ROOT/bin:$HOME/.local/bin:$PATH"

eval "$(pyenv init - bash)"

eval "$(pyenv virtualenv-init -)"

eval "$(oh-my-posh init bash --config ~/.cache/oh-my-posh/themes/atomic.omp.json)"

EOF'

# Chain pyenv commands in one shell with explicit env setup

- |

su - powercommons -c 'export PYENV_ROOT="$HOME/.pyenv" && \

export PATH="$PYENV_ROOT/bin:$HOME/.local/bin:$PATH" && \

eval "$(pyenv init -)" && \

pyenv install 3.12 && \

pyenv virtualenv 3.12 microwatt'

- su - powercommons -c 'mkdir -p projects && cd projects && git clone https://codeberg.org/PowerCommons/microwatt.git'

# LiteX in activated venv

- |

su - powercommons -c 'export PYENV_ROOT="$HOME/.pyenv" && \

export PATH="$PYENV_ROOT/bin:$HOME/.local/bin:$PATH" && \

eval "$(pyenv init -)" && \

eval "$(pyenv virtualenv-init -)" && \

pyenv activate microwatt && \

pip3 install --upgrade fusesoc && \

mkdir -p ~/projects/litex && cd ~/projects/litex && \

wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py && \

chmod +x litex_setup.py && \

./litex_setup.py --init --install --config=standard'

- sudo ln -s /usr/lib/x86_64-linux-gnu/libcurses.so /lib64/libncurses.so.6

- sudo ln -s /usr/lib/x86_64-linux-gnu/libtinfo.so /lib64/libtinfo.so.5

Next, open a Windows Terminal or Powershell and run the following command. Note that the name of the distribution must match the name of the file you created above.

wsl --install -d Ubuntu-24.04 --name PowerCommons

Once the process completes, you will be logged into your new WSL instance.

Note

The cloud-config will:

- Create a user named powercommons with the password powercommons and set it as default via /etc/wsl.conf

- Create a python virtual environment called microwatt

- Install all required packages and dependencies as listed in the

packagessection of the yml config above.- The script will create a folder called projects in the home folder of the user

powercommons, clone microwatt repository, and install Litex with standard distribution.

Feel free to explore the yml configuration script above to understand what is installed and configured.

Creating an Ubuntu WSL 2 Instance - Manual installation

If you want to install and configure your WSL instance manually, you can run wsl --install -d Ubuntu-24.04 --name PowerCommonsA2OISAUpgrade. :

> wsl --install -d Ubuntu-24.04 --name PowerCommonsA2OISAUpgrade

Downloading: Ubuntu 24.04 LTS

Installing: Ubuntu 24.04 LTS

Distribution successfully installed. It can be launched via 'wsl.exe -d PowerCommonsA2OISAUpgrade'

Launching PowerCommonsA2OISAUpgrade...

Provisioning the new WSL instance PowerCommonsA2OISAUpgrade

This might take a while...

Create a default Unix user account: power2people

New password:

Retype new password:

passwd: password updated successfully

To run a command as administrator (user "root"), use "sudo <command>".

See "man sudo_root" for details.

power2people@DESKTOP-P4O:/mnt/c/Users/anonymous$

Choose a username and a password when prompted and save it in a password manager - you will need it later. In the example above, we used power2people as the username. Once the process finishes, you will be logged in to the new instance and land at the shello.

This process will also install a shortcut by the name of PowerCommonsA2OISAUpgrade in your start menu in Windows. You can use this shortcut to launch the PowerCommonsA2OISAUpgrade Ubuntu instance later or after a restart.

Note that multiple shells can be opened simultaneously without interfering with each other. Refer to Ubuntu’s WSL documentation for details.

Creating multiple WSL instances

If you are going to be working on multiple projects, it is highly recommended to create multiple WSL 2 instances - one for each project to avoid mixing up libraries and for isolation. To creat a second instance using Ubuntu, just change the --name parameter for you new installation. For instance, you can have three WSL instaces - each dedicated to a specific project:

wsl --install -d Ubuntu-24.04 --name A2ORevival: Creates an instance for A2O Revival project.wsl --install -d Ubuntu-24.04 --name A2OISAUpgrade: Creates an instance for A2O Upgrade project.wsl --install -d Ubuntu-24.04 --name Microwatt: Creates an instance for Microwatt project.

Next Steps

Vivado Installation

Vivado is required for synthesizing bitstream for FPGAs - both for Microwatt and for A2O.

The following steps are derived from the Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973)

Downloading Vivado

Download Vivado 2025.2 from AMD/Xilinx. This will require you to register and provide your details before downloading. All PowerCommons projects are built and tested with Vivado 2025.2. It is recommended to download the Single File Download if you will be creating multiple WSL instances - it will save you significant amount of time as you dowload the installer only once. However, this requires more disk space. If you don’t have a fast internet connection or have limited disk space, you can download the Unified Web installer for Linux.

Note

You need to dowload the Linux version even if you are using Windows as you main operating system. We will copy the installer to WSL Linux once we’re ready to install.

Assuming you are on Windows and downloaded the installer to `C:\Downloads\FPGAs_AdaptiveSoCs_Unified_SDI_2025.2_1114_2157.tar“, copy the installer to WSL instance. You can do it by running the following command from inside WSL Debian instance:

>cp /mnt/C/Downloads/FPGAs_AdaptiveSoCs_Unified_SDI_2025.2_1114_2157.tar ~

or if you downloaded the web installer:

>cp /mnt/C/Downloads/FPGAs_AdaptiveSoCs_Unified_SDI_2025.2_1114_2157_Lin64.bin ~

This will copy the installer to your home directory in WSL 2 Debian instance. Note this might take a few minutes depending upon your disk speed.

Installing Vivado Prerequisites

Before you actually install Vivado in your WSL 2 instance, install the prerequisites. In many cases, the installer can fail if the required libraries are missing. Vivado 2025 includes a script to check for and install any missing libraries. For both the Unified Single File Download (SFD) and the Webinstaller, the installLibs.sh script is located at the image root. To access the image root area with the Webinstaller, use the following command in batch mode on a Linux machine to extract the image.

><Download_Dir>/FPGAs_AdaptiveSoCs_Unified_202X.Y_MMDD_HHMM_Lin64.bin –keep --noexec --target <WI_Client_Dir>

Replace <WI_Client_Dir> with the target directory where you want to extract the files. Alternatively, if you are using the tar file, you can extract the files as shown below:

> tar -xvf FPGAs_AdaptiveSoCs_Unified_SDI_2025.2_1114_2157.tar

Once the files are extracted, you will find a script called installLibs.sh. This script will install all the libraries required for Vivado installation.

> cd FPGAs_AdaptiveSoCs_Unified_SDI_2025.2_1114_2157

> sudo ./installLibs.sh

[sudo] password for power2people:

ubuntu-24 install

Hit:1 http://archive.ubuntu.com/ubuntu noble InRelease

Get:2 http://archive.ubuntu.com/ubuntu noble-updates InRelease [126 kB]

Get:3 http://security.ubuntu.com/ubuntu noble-security InRelease [126 kB]

Get:4 http://archive.ubuntu.com/ubuntu noble-backports InRelease [126 kB]

Get:5 http://archive.ubuntu.com/ubuntu noble/universe amd64 Packages [15.0 MB]

Get:6 http://archive.ubuntu.com/ubuntu noble/universe Translation-en [5982 kB]

....

....

Preparing to unpack .../5-libsecret-1-dev_0.21.4-1build3_amd64.deb ...

Unpacking libsecret-1-dev:amd64 (0.21.4-1build3) ...

Setting up libgpg-error-dev (1.47-3build2.1) ...

Setting up libsecret-common (0.21.4-1build3) ...

Setting up libsecret-1-0:amd64 (0.21.4-1build3) ...

Setting up gir1.2-secret-1:amd64 (0.21.4-1build3) ...

Setting up libgcrypt20-dev (1.10.3-2build1) ...

Setting up libsecret-1-dev:amd64 (0.21.4-1build3) ...

Processing triggers for libc-bin (2.39-0ubuntu8.6) ...

Processing triggers for man-db (2.12.0-4build2) ...

Processing triggers for install-info (7.1-3build2) ...

INFO: For more information please check /home/power2people/FPGAs_AdaptiveSoCs_Unified_SDI_2025.2_1114_2157/installLibs.sh_2025-12-13_15-36-28 log.

Now you are ready to install Vivado.

Vivado Installation

To launch the vivado installer, lanunch the installer binary as shown below:

> sudo chmod +x FPGAs_AdaptiveSoCs_Unified_20XX.Y_MMDD_HHMM_Lin64.bin

> ./FPGAs_AdaptiveSoCs_Unified_20XX.Y_MMDD_HHMM_Lin64.bin

Alternatively, if you downloaded the SDI tar file, launch the installer from the folder (FPGAs_AdaptiveSoCs_Unified_SDI_2025.2_1114_2157) extracted above:

>./xsetup

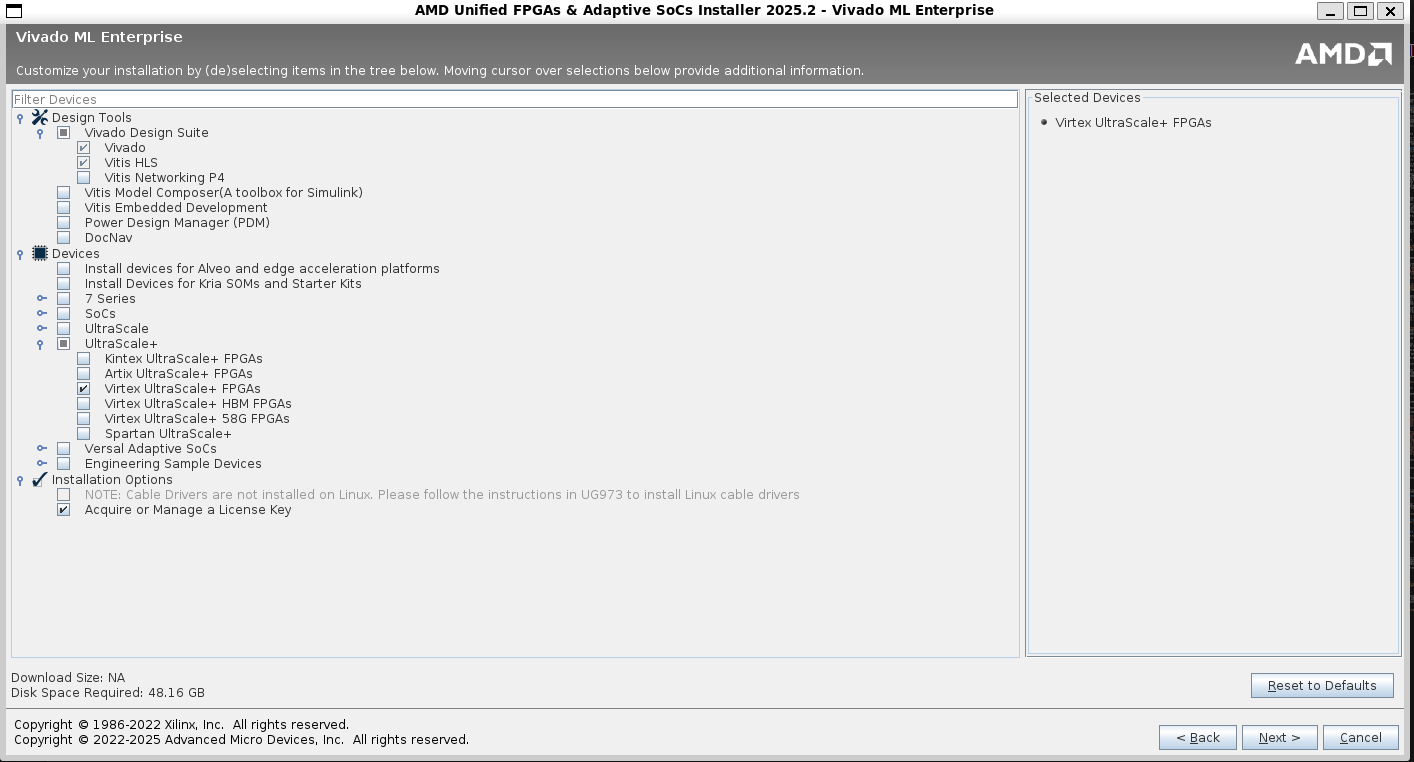

From the list of products to install, select Vivado. Note that you only need Vivado to work with PowerCommons projects - you don’t need Vitis or any other products. On the next screen, choose Vivado ML Enterprise if you have a license or alternatively choose Vivado ML standard. Remove any unnecessary Vitis or other components - you only need the minimum components as shown below along with components specific to your FPGA device (Ultrascale+ in this case).

Click next to continue.

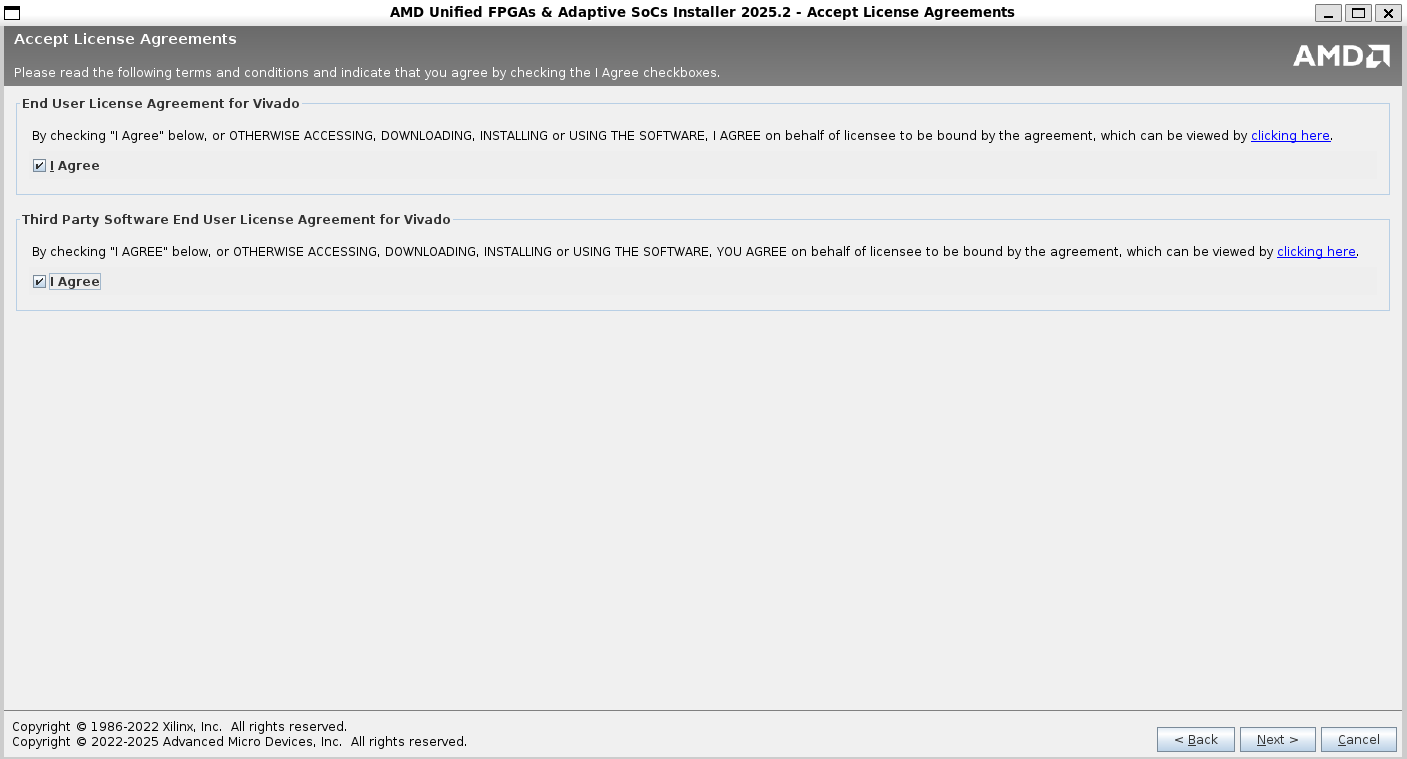

Accept the license and usage terms, click next to continue.

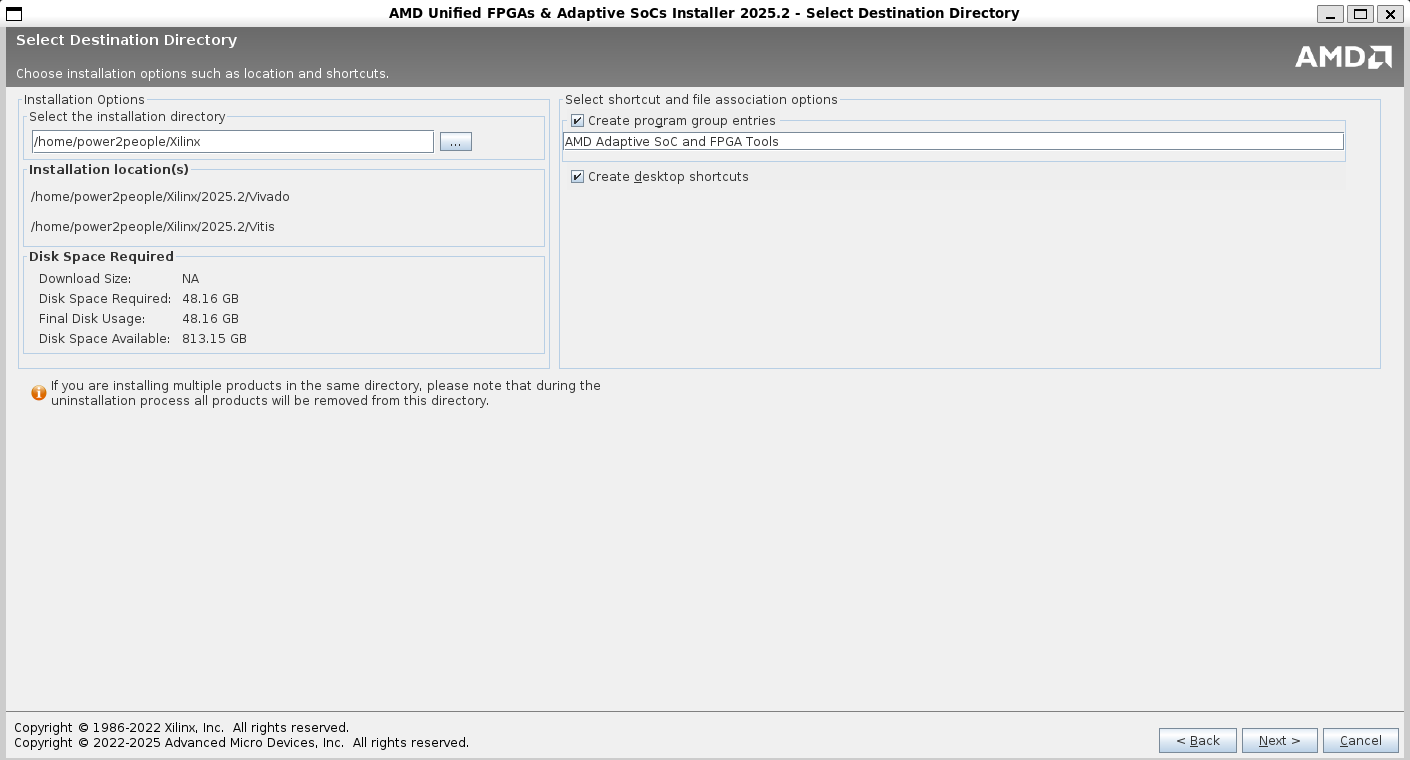

Specify an installation directory and click next to continue.

Review the installation summary and click Install to start the installation. Wait for the installer to download the files in case you are using web installer - it can take 30-60 minutes or even longer on slower internet connections.

Setting up Vivado Paths for terminal utilities

Once the installation is complete, add Vivado to your path. The following assumes you are using bash on WSL 2 but the process is similar for other shells too:

# Open your .bashrc file in vim editor

> echo 'source <PathToXilinxInstallationDIR>/Vivado/2025.2/settings64.sh' >> ~/.bashrc

Replace PathToXilinxInstallationDIR with the path to Xilinx installation folder from the previous step.

Installing USB drivers and pass through on Windows

The final step in Vivado installation on WSL is to allow USB passthrough from Windows to WSL 2.

Install USBIPD on Windows 11

Note

Vivado is not supported on ARM platforms. Please make sure you download the installer for your AMD/Intel based machines.

Go to the USBIPD Release Page and download the latest x64 installer for Windows. You may get a warning asking you to confirm that you trust this download. Run the downloaded usbipd-win_x.msi installer file. Running the installer will install:

- A service called usbipd (display name: USBIP Device Host). You can check the status of this service using the Services app from Windows.

- A command line tool usbipd. The location of this tool will be added to the PATH environment variable.

- A firewall rule called usbipd to allow all local subnets to connect to the service. You can modify this firewall rule to fine tune access control.

List all of the USB devices connected to Windows by opening PowerShell in administrator mode and entering the following command. Once the devices are listed, select and copy the bus ID of the device you’d like to attach to WSL.

usbipd list

Before attaching the USB device, the command usbipd bind must be used to share the device, allowing it to be attached to WSL. This requires administrator privileges. Select the bus ID of the device you would like to use in WSL and run the following command. After running the command, verify that the device is shared using the command usbipd list again.

usbipd bind --busid 4-4

To attach the USB device, run the following command. (You no longer need to use an elevated administrator prompt.) Ensure that a WSL command prompt is open in order to keep the WSL 2 lightweight VM active. Note that as long as the USB device is attached to WSL, it cannot be used by Windows. Once attached to WSL, the USB device can be used by any distribution running as WSL 2. Verify that the device is attached using usbipd list. From the WSL prompt, run lsusb to verify that the USB device is listed and can be interacted with using Linux tools.

usbipd attach --wsl --busid <busid>

Open Ubuntu (or your preferred WSL command line) and list the attached USB devices using the command:

>lsusb

You should see the device you just attached and be able to interact with it using normal Linux tools. This should be sufficient to access the device from Vivado and other utilities. However, in some cases, you may need to configure udev rules to allow non-root users to access the device.

Once you are done using the device in WSL, you can either physically disconnect the USB device or run this command from PowerShell:

usbipd detach --busid <busid>

To learn more about how this works, see the Windows Command Line Blog and the usbipd-win repo on GitHub.

Warning

You will have re-bind the USB device if you re-start or disconnect your FPGA board.

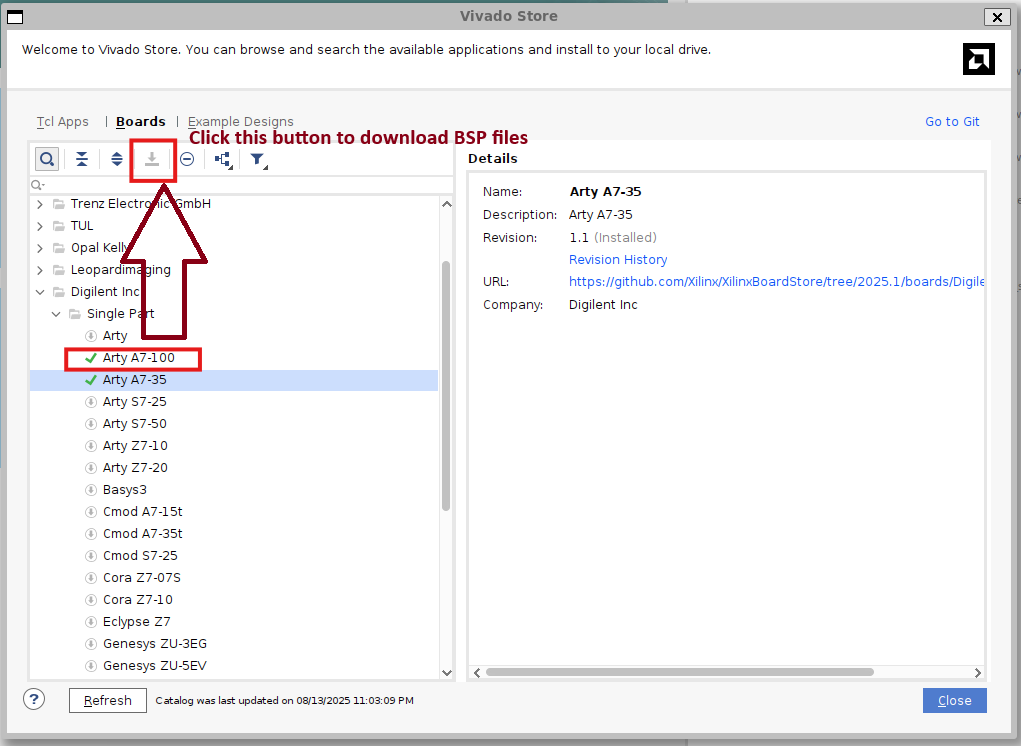

Install Digilent Board files

This step is only required if you are using any of Digilent Boards such as Arty A7 100T. If you are using Xilinx boards such as VCU-118, skip this step.

To install BSP files, launch vivado from WSL:

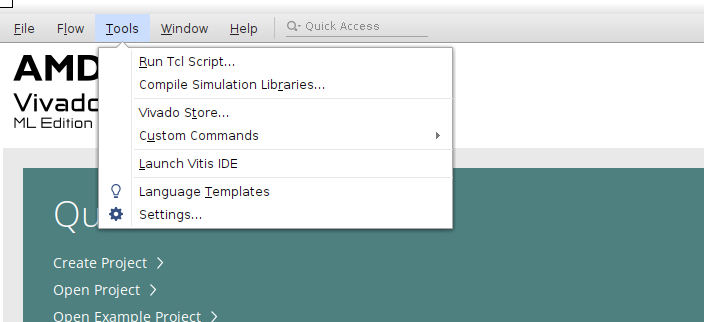

>vivado

Once Vivado starts, select Vivado Store from the Tools menu:

Check the “Don’t show this dialog again” checkbox and click ok.

In the Vivado Store Window, click on “Boards Tab”. In the left tree pane, look for Digilent Inc. Expand the tree node and then expand the child “Single Part” tree node and look for your device. For example, if you are installing for Arty A7 100T, select the device from the tree and click on Download button on the top. Once the donwload button finishes, you will see a green tick against the device name indicating the BSP files have been installed. Click close and exist the Vivado Store.

Next Steps

Version Compatibility

PowerCommons projects target Vivado 2025.x. Using older versions (2023.x, 2024.x) may require constraint updates.

LiteX Setup

LiteX SoC builder framework for generating DDR controllers, peripherals, and SoC infrastructure.

Installation

1. Install LiteX

# Using pip (recommended)

pip3 install --user litex litex-boards

# Verify

python3 -c "import litex; print(litex.__version__)"

2. Clone LiteX Ecosystem (for development)

mkdir ~/litex && cd ~/litex

wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

chmod +x litex_setup.py

./litex_setup.py --init --install --user

This installs:

litex- Core frameworklitex-boards- Board definitionslitedram- DDR controller generatorliteeth- Ethernet MAC/PHYlitepcie- PCIe controllerlitesata- SATA controller

Test LiteX

Generate a simple SoC

# For VCU-118

litex_soc --board vcu118 --cpu-type microwatt --build

# For Arty A7

litex_soc --board arty --cpu-type vexriscv --build

Build time: ~5-10 minutes.

LiteDRAM for DDR4

PowerCommons uses LiteDRAM for VCU-118 DDR4 memory.

Test DDR4 initialization

cd ~/litex/litedram

./litedram_gen.py --sdram-module MT40A512M16 --sdram-data-width 64

PowerPC Support in LiteX

PowerCommons has contributed Microwatt (PowerPC) CPU support to LiteX.

Check CPU options

litex_soc --cpu-list | grep -i power

Expected output:

microwatt

Configuration for VCU-118

Example build command:

litex_soc \

--board vcu118 \

--cpu-type microwatt \

--cpu-variant standard \

--sys-clk-freq 100e6 \

--integrated-rom-size 0x10000 \

--integrated-sram-size 0x2000 \

--with-ethernet \

--build

Output: build/vcu118/gateware/vcu118.bit

Directory Structure

~/litex/

├── litex/ # Core framework

├── litex-boards/ # Board support

├── litedram/ # DDR controllers

├── liteeth/ # Ethernet

├── litepcie/ # PCIe

└── litesata/ # SATA

Environment Variables

Add to ~/.bashrc:

export PATH=$HOME/.local/bin:$PATH

export LITEX_BOARDS=$HOME/litex/litex-boards

Common Issues

“Command not found: litex_soc”

export PATH=$HOME/.local/bin:$PATH

“Board not found”

pip3 install --user --upgrade litex-boards

Synthesis errors with Vivado Ensure Vivado is in PATH:

source /opt/Xilinx/Vivado/2025.1/settings64.sh

Advanced: Custom SoC Configuration

Create soc_config.py:

from litex_boards.targets import vcu118

from litex.soc.cores.cpu import Microwatt

class CustomSoC(vcu118.BaseSoC):

def __init__(self):

super().__init__(

cpu_type="microwatt",

sys_clk_freq=125e6,

with_ethernet=True

)

if __name__ == "__main__":

soc = CustomSoC()

soc.build()

Run:

python3 soc_config.py

Documentation

- LiteX Wiki: github.com/enjoy-digital/litex/wiki

- PowerCommons LiteX integration: Projects → Microwatt → LiteX Integration

Next Steps

PowerPC Toolchain

This page describes the tool chain and compilers needed to build Linux and other binaries for PowerPC architectures (Microwatt, A2O, A2I etc.). This page also serves as an introduction to all cross compile packages and utilities that are available to anyone developing for PPC64 architecture.

Overview

As more experienced users might already know, PowerPC compilers and utilities are available into both Big Endian and Little Endian formats. The most popular formats these days is Little Endian and PowerCommons projects use Little Endian formats.

PowerPC64 Little-Endian (LE) Cross-Compilation Toolchain

| Package | Purpose | Install |

|---|---|---|

gcc-powerpc64le-linux-gnu | C cross-compiler | sudo apt install gcc-powerpc64le-linux-gnu |

g++-powerpc64le-linux-gnu | C++ cross-compiler | sudo apt install g++-powerpc64le-linux-gnu |

binutils-powerpc64le-linux-gnu | Linker, assembler, objdump | sudo apt install binutils-powerpc64le-linux-gnu |

libc6-dev-ppc64el-cross | C library headers & dev files | sudo apt install libc6-dev-ppc64el-cross |

linux-libc-dev-ppc64el-cross | Linux kernel UAPI headers | sudo apt install linux-libc-dev-ppc64el-cross |

gdb-multiarch | Multi-target debugger | sudo apt install gdb-multiarch |

qemu-user-static | Userspace emulation for ppc64le | sudo apt install qemu-user-static |

Install:

sudo apt install gcc-powerpc64le-linux-gnu g++-powerpc64le-linux-gnu binutils-powerpc64le-linux-gnu libc6-dev-ppc64el-cross linux-libc-dev-ppc64el-cross gdb-multiarch qemu-user-static

Verify:

powerpc64-linux-gnu-gcc --version

PowerPC64 Big-Endian (BE) Cross-Compilation Toolchain

| Package | Purpose | Install |

|---|---|---|

gcc-powerpc64-linux-gnu | C cross-compiler | sudo apt install gcc-powerpc64-linux-gnu |

g++-powerpc64-linux-gnu | C++ cross-compiler | sudo apt install g++-powerpc64-linux-gnu |

binutils-powerpc64-linux-gnu | Linker, assembler, objdump | sudo apt install binutils-powerpc64-linux-gnu |

libc6-dev-ppc64-cross | C library headers & dev files | sudo apt install libc6-dev-ppc64-cross |

linux-libc-dev-ppc64-cross | Linux kernel UAPI headers | sudo apt install linux-libc-dev-ppc64-cross |

gdb-multiarch | Multi-target debugger | sudo apt install gdb-multiarch |

qemu-user-static | Userspace emulation for ppc64 | sudo apt install qemu-user-static |

Install:

sudo apt install gcc-powerpc64-linux-gnu g++-powerpc64-linux-gnu binutils-powerpc64-linux-gnu libc6-dev-ppc64-cross linux-libc-dev-ppc64-cross gdb-multiarch qemu-user-static

Verify:

powerpc64-linux-gnu-gcc --version

Test Cross-Compilation

Hello World

// hello.c

#include <stdio.h>

int main() {

printf("Hello from PowerPC!\n");

return 0;

}

Compile:

powerpc64-linux-gnu-gcc -o hello hello.c

file hello

Expected:

hello: ELF 64-bit MSB executable, 64-bit PowerPC

First Bitstream Build

Complete guide to building and booting Linux on Microwatt with the VCU-118 FPGA.

Prerequisites: This guide assumes you are using the official PowerCommons WSL images and have followed all instructions in the Development Environment section.

Overview

Build and boot Linux on VCU-118 in four steps:

- Build Buildroot (cross-compiler + userspace)

- Build Linux kernel (with Microwatt patches)

- Build FPGA bitstream (Microwatt + DDR4 + QSPI)

- Flash and boot

Clone Repositories

cd ~/projects

# Microwatt with VCU-118 support

git clone https://codeberg.org/PowerCommons/microwatt.git

cd microwatt

git checkout xilinx-vcu-118-dram

cd ..

# Linux kernel (upstream v6.12)

git clone --depth=1 --branch v6.12 \

https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git linux

# PowerCommons kernel patches

git clone https://codeberg.org/PowerCommons/linux-powercommons.git

# Buildroot for userspace

git clone https://github.com/shenki/buildroot -b microwatt buildroot-microwatt

Step 1: Build Buildroot

Build the cross-compiler and root filesystem:

cd ~/projects/buildroot-microwatt

make ppc64le_microwatt_defconfig

make -j$(nproc)

Build time: ~30 minutes

Output:

- Cross-compiler:

output/host/bin/powerpc64le-buildroot-linux-gnu-gcc - Root filesystem:

output/images/rootfs.cpio

Step 2: Build Linux Kernel

Apply PowerCommons Patches

cd ~/projects/linux

git am ~/projects/linux-powercommons/patches/microwatt-vcu118/*.patch

This applies the RCU fix and device tree updates needed for Microwatt on VCU-118. See the Microwatt Kernel RCU Fix blog post for details on why this is needed.

Configure Kernel

make ARCH=powerpc microwatt_defconfig

Set Initramfs Path

Edit .config and set the path to your rootfs.cpio:

CONFIG_INITRAMFS_SOURCE="/home/powercommons/projects/buildroot-microwatt/output/images/rootfs.cpio"

Build Kernel

export PATH="/home/powercommons/projects/buildroot-microwatt/output/host/bin:$PATH"

make ARCH=powerpc CROSS_COMPILE=powerpc64le-buildroot-linux-gnu- -j$(nproc) zImage

Build time: ~5 minutes

Output: arch/powerpc/boot/dtbImage.microwatt.elf

Step 3: Build FPGA Bitstream

Generate LiteDRAM Core

cd ~/projects/microwatt/litedram/gen-src

python3 generate.py xilinx-vcu-118

Build Bitstream

cd ~/projects/microwatt

fusesoc library add microwatt .

fusesoc run --target=xilinx-vcu-118 microwatt --no_bram --spi_flash_offset=33554432

Parameters:

--no_bram: Boot from external flash instead of internal BRAM--spi_flash_offset=33554432: Linux kernel location at 32MB offset

Build time: ~45 minutes

Output: build/microwatt_0/xilinx-vcu-118-vivado/microwatt_0.bit

Step 4: Flash and Boot

Program Bitstream

openFPGALoader -b vcu118 --write-flash ~/projects/microwatt/build/microwatt_0/xilinx-vcu-118-vivado/microwatt_0.bit

Program Linux Kernel (at 32MB offset)

openFPGALoader -b vcu118 --write-flash -o 0x2000000 ~/projects/linux/arch/powerpc/boot/dtbImage.microwatt.elf

Connect Serial Console

tio /dev/ttyUSB0 -b 115200

Power Cycle

Power cycle the VCU-118 board. You should see:

Welcome to Microwatt !

Soc signature: f00daa5500010001

Soc features: UART DRAM SPIFLASH

DRAM: 2047 MB

CLK: 125 MHz

SPI FLASH ID: 20bb21 Micron 1G [quad IO mode]

LiteDRAM built from LiteX f55ea7075

Initializing SDRAM @0x40000000...

Memtest OK

Trying flash...

Booting from DRAM at 1700000

[... Linux boot messages ...]

Welcome to Buildroot

microwatt login:

Login with root (no password).

Troubleshooting

| Problem | Solution |

|---|---|

| SPI FLASH ID: 000000 | Check STARTUPE3 DO/DI wiring. See QSPI blog post |

| Kernel crashes in rcu_process_callbacks | Apply the PowerCommons patches. See RCU fix blog post |

| “Can’t open blockdev” | Set CONFIG_INITRAMFS_SOURCE to your rootfs.cpio path |

| DDR4 training fails | Check clock stability and reset sequencing |

Repository Links

- Microwatt: codeberg.org/PowerCommons/microwatt (branch:

xilinx-vcu-118-dram) - Kernel Patches: codeberg.org/PowerCommons/linux-powercommons

- Buildroot: github.com/shenki/buildroot (branch:

microwatt)

Troubleshooting

Common issues and solutions.

Environment Setup

Vivado Not Found

Symptom: vivado: command not found

Solution:

source /opt/Xilinx/Vivado/2025.1/settings64.sh

# Make permanent

echo 'source /opt/Xilinx/Vivado/2025.1/settings64.sh' >> ~/.bashrc

Python Import Errors

Symptom: ModuleNotFoundError: No module named 'litex'

Solution:

pip3 install --user litex litex-boards

export PATH=$HOME/.local/bin:$PATH

USB Permission Denied

Symptom: Error: libusb_open() failed with LIBUSB_ERROR_ACCESS

Solution:

# Temporary

sudo chmod 666 /dev/ttyUSB*

# Permanent

sudo usermod -a -G dialout $USER

# Logout and login

Build Errors

Synthesis Fails - Timing

Symptom:

CRITICAL WARNING: Timing constraints are not met

WNS: -1.234ns

Solution:

Reduce clock frequency:

# LiteX

python3 vcu118.py --sys-clk-freq=80e6 # Was 100e6

Out of Memory

Symptom: Build crashes, system freezes

Solution:

# Limit parallel jobs

export MAKEFLAGS="-j2"

# Increase swap

sudo fallocate -l 16G /swapfile

sudo chmod 600 /swapfile

sudo mkswap /swapfile

sudo swapon /swapfile

License Error

Symptom: License checkout failed

Solution:

# Check license

echo $XILINXD_LICENSE_FILE

# Or run license manager

vlm &

For VCU-118, you need Standard edition license (eval or purchased). WebPACK doesn’t support Ultrascale+.

Missing FPGA Part

Symptom: Part xcvu9p not found

Solution:

Re-run installer to add Ultrascale+ device support:

sudo /opt/Xilinx/Vivado/2025.1/xsetup

FPGA Programming

Cable Not Detected

Symptom: No devices detected

Solution:

- Check USB connection:

lsusb | grep Xilinx

- Install cable drivers:

cd /opt/Xilinx/Vivado/2025.1/data/xicom/cable_drivers/lin64/install_script/install_drivers

sudo ./install_drivers

- WSL users - USB passthrough:

usbipd list

usbipd attach --wsl --busid X-X

Programming Fails

Symptom: Programming failed at 30%

Solution:

- Check power supply to board

- Verify correct .bit file for board

- Try lower JTAG frequency:

openocd -c "adapter speed 1000" -f board/vcu118.cfg

Serial Console

No Output

Symptom: Screen is blank after programming

Solution:

- Check baud rate:

screen /dev/ttyUSB1 115200 # Not 9600

- Check correct USB port:

ls -l /dev/ttyUSB*

# Usually ttyUSB0 = JTAG, ttyUSB1 = UART

- Check FPGA programmed:

- Look for LEDs on board

- Run

lsusb, should show Xilinx device

- Try reset:

- Press reset button on board

- Power cycle

Garbled Output

Symptom: Random characters

Solution:

Clock frequency mismatch. Check UART clock divider matches system clock.

Boot Issues

Linux Kernel Panics

Symptom:

Kernel panic - not syncing: VFS: Unable to mount root fs

Solution:

- Check device tree:

dtc -I dtb -O dts microwatt.dtb | grep memory

- Verify initrd:

file rootfs.cpio.gz

# Should be gzip compressed

- Check bootargs:

console=ttyS0,115200 root=/dev/ram0

Hangs at Boot

Symptom: Boot stops at “Starting kernel…”

Solution:

- Enable early printk in kernel config

- Check memory controller initialization

- Verify DDR4 timing constraints

LiteX Specific

Build Fails - Yosys

Symptom: Yosys not found

Solution:

cd ~/litex

./litex_setup.py --install --user

SoC Build Fails - Missing Board

Symptom: Board vcu118 not found

Solution:

pip3 install --user --upgrade litex-boards

Performance Issues

WSL Builds Slow

Symptom: Build takes 3x longer than expected

Solution:

Move project to WSL filesystem:

# Bad (slow)

cd /mnt/c/Users/name/projects

# Good (fast)

cd ~/projects

File I/O across WSL/Windows boundary is slow.

Vivado GUI Sluggish

Symptom: Vivado GUI freezes, slow

Solution:

- Use batch mode when possible:

vivado -mode batch -source build.tcl

- Resource limits:

Ensure WSL has enough RAM (see

.wslconfig)

Getting Help

Still stuck?

- Check logs:

cat build/*/vivado.log

- Community:

- Matrix: #powercommons:matrix.org

- Codeberg: codeberg.org/PowerCommons

- Upstream:

- Microwatt: github.com/antonblanchard/microwatt

- LiteX: github.com/enjoy-digital/litex/wiki

- Vivado: xilinx.com/support

- Provide details:

- OS and version

- Vivado version

- Complete error log

- Steps to reproduce

Projects Overview

Building the Open Computing Stack

PowerCommons develops interconnected projects that together create a complete, transparent, and sovereign computing platform. Each project advances specific technical goals while contributing to the larger vision of liberation technology.

Core Processor Projects

✅ Microwatt Xilinx VCU-118 Integration

Status: In Progress | Estimate: October 2025

Successfully integrated Microwatt processor with enterprise-grade Xilinx VCU-118 board, enabling Linux boot.

Achievements: ✅ Added VCU-118 support to Microwatt SoC (FuseSoC + VHDL). This additionally sets up LEDs to debug issues with clock, reset signal, UART etc. ✅ Extended Microwatt SoC LiteDRAM support to VCU-118 board 🟡 Fixed LitexBios and LitexSoC to support Linux on Microwatt as Litex BIOS was only designed to boot RISC V.

Why It Matters: Established VCU-118 as the primary development platform for high-end OpenPower FPGA work.

🔥 PowerCommons A2O: OpenPower A2O Core Revival

Status: Active Development | Target: Q4 2025

Reviving IBM’s battle-tested A2O processor - the out-of-order superscalar core that powered Blue Gene/Q supercomputers. This enterprise-grade processor brings serious computational power to the open hardware ecosystem.

Key Objectives:

- Restore compatibility with modern FPGA toolchains

- Fix timing closure and synthesis issues

- Create comprehensive documentation

- Establish software toolchain

Why It Matters: A2O provides the high-performance computing capability needed for real-world workloads, from scientific computing to database servers.

🏗️ PowerCommons SoC Platform

Status: Architecture Phase | Target: 2026

Creating the world’s first fully open System-on-Chip with verifiable security from boot to application. Combines Microwatt (control) and A2O (compute) processors in a heterogeneous architecture.

Key Objectives:

- Integrate dual-core heterogeneous design

- Implement open BMC replacement

- Create secure boot architecture

- Develop complete firmware stack

Why It Matters: Eliminates the last proprietary components in modern computing systems, including the hidden management engines.

Project Integration Strategy

┌─────────────────────────────────────────────┐

│ PowerCommons Platform │

├─────────────────────────────────────────────┤

│ │

│ ┌─────────────┐ ┌─────────────┐ │

│ │ Microwatt │◄────►│ A2O │ │

│ │ (Boot) │ │ (Compute) │ │

│ └─────────────┘ └─────────────┘ │

│ ▲ ▲ │

│ └────────┬───────────┘ │

│ ▼ │

│ ┌─────────────┐ │

│ │ LiteX │ │

│ │ Framework │ │

│ └─────────────┘ │

│ ▼ │

│ ┌──────────────────────────────────┐ │

│ │ Peripherals & Memory │ │

│ └──────────────────────────────────┘ │

│ │

└─────────────────────────────────────────────┘

“The future is not some place we are going, but one we are creating. The paths are not to be found, but made.” - John Schaar

Microwatt Integration

Open PowerPC Core on Modern FPGAs

Overview

Microwatt is an open-source PowerPC soft core developed by Anton Blanchard and IBM. PowerCommons has extended Microwatt to run on high end FPGA platforms with full Linux support.

Core: Microwatt v0.1

Architecture: PowerPC 64-bit

Platform: Xilinx VCU-118

Status: Linux operational

Development Work

Native Microwatt SoC

Implementation using Microwatt’s native build system (FuseSoC/VHDL):

- VCU-118 board support with debug capabilities

- DDR4 memory integration via LiteDRAM

- Linux boot from native Microwatt

LiteX Framework Integration

Integration of Microwatt into LiteX SoC framework:

- PowerPC support in LiteX BIOS

- Endianness and boot protocol fixes

- Linux boot through LiteX infrastructure

Key Achievements

| Metric | Result |

|---|---|

| Clock Speed | 125MHz |

| Memory | 2GB DDR4 |

| Linux Boot | + seconds |

| Stability | + hours |

Upstream Contributions

- Microwatt: VCU-118 platform support

- LiteX: PowerPC architecture fixes

- LiteDRAM: DDR4 timing configurations

Resources

Microwatt SoC on VCU-118

Overview

Implementation of Microwatt SoC on Xilinx VCU-118 using the native Microwatt build system (FuseSoC/VHDL). This work establishes basic board support, DDR4 and debugging capabilities.